Anantharaj

I'm CMOS & Non-Volatile Memory Design Verification Expert

About

CMOS VLSI and NAND Flash Memory Design Verification Expert, QCA & Hardware Security Researcher, Senior Member IEEE, IETE Fellow, BCS Fellow, FuSa Certified, Editorial Board Member.

CMOS & Non-Volatile Memory Design Verification Expert

Data driven, result oriented leader with passion for functional verification and innovation infused execution.

- Email: [email protected]

- Website: www.example.com

- Phone: +1-341-345-2659

- Email: [email protected]

- City: San Jose, California, USA

- Degree: B.E(ECE)., M.Tech (VLSI System), Ph.D (Post-CMOS QCA Designs)

- Specilazation: Non-Volatile Memory, CMOS VLSI and QCA Designs.

INNOVATION

Cross Functional CollaborationPatents and Trade Secrets

Conferences and Publications

US Patents

Trade Secrets

Publications

Manuscripts Reviewed

Citations

Skills

| Technologies and Tools | ||

|---|---|---|

| Verilog | System Verilog | System Verilog Assertions (SVA) |

| Universal Verification Methodology (UVM) | Formal Techniques | EDA Tools |

| ONFI,PCIe | DDR, SAS, CXL | C++ Python |

Resume Download

Data driven, result oriented leader with passion for functional verification and innovation infused execution.

Sumary

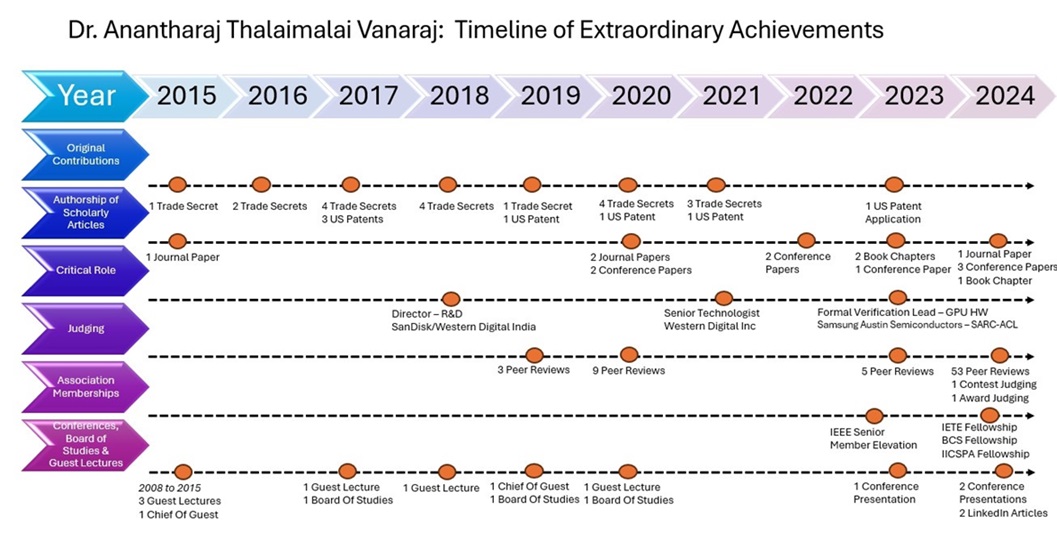

Dr. ANANTHARAJ THALAIMALAI VANARAJ

Innovative and result oriented Design Verification professional with 20 years of experience

- At San Jose, California

- +1-341-345-2659

- [email protected]

Education

DOCTOR OF PHILOSOPHY

QUANTUM-DOT CELLULAR AUTOMATA (QCA)

MASTER OF TECHNOLOGY

VLSI SYSTEM

2002 - 2004

National Institute of Technology, Trichy, Tamilnadu, India

BACHELOR OF ENGINEERING

ELECTRONICS AND COMMUNICATION

1998 - 2002

Thanthai Periyar Government Institute of Technology (TPGIT), Madras University, Tamilnadu, India

Professional Experience

FORMAL VERIFICATION LEAD

AUG 2023 - PRESENT

Samsung Austin Semiconductors – Advanced Computing Lab

- Formal Verification ownership for GPU RTL blocks; Mentoring members; JIRA driven task planning and resource estimation; Metrics based project reporting.

DIRECTOR/SENIOR TECHNOLOGIST

SEP 2008 – JULY 2023

Western Digital Technologies (SanDisk), Milpitas/Bangalore

- Established Front End Design group for NAND Flash Memory development; Mentored team of 35+ engineers for RTL Design, Verification and Modeling; Developed and tracked KPIs for verification signoff; Handled verification closure using UVM and Formal Methodologies.

- Deployed Zero Bug escape strategy across 10+ tape outs; Initiated System and Firmware level collaboration; Led JIRA/EazyBI dashboard reporting; Optimized verification regressions; Owned group level project planning, resource estimation and task scheduling for 2D/3D NAND Designs

VERIFICATION LEAD/SENIOR ENGINEER

JUL 2004 – AUG 2008

Wipro E-Peripherals, Samsung and LSI Logic India, Bangalore/Mysore

- Played key role in System Verilog based verification of FPGA/ASIC designs for computer peripherals, wireless and storage controllers

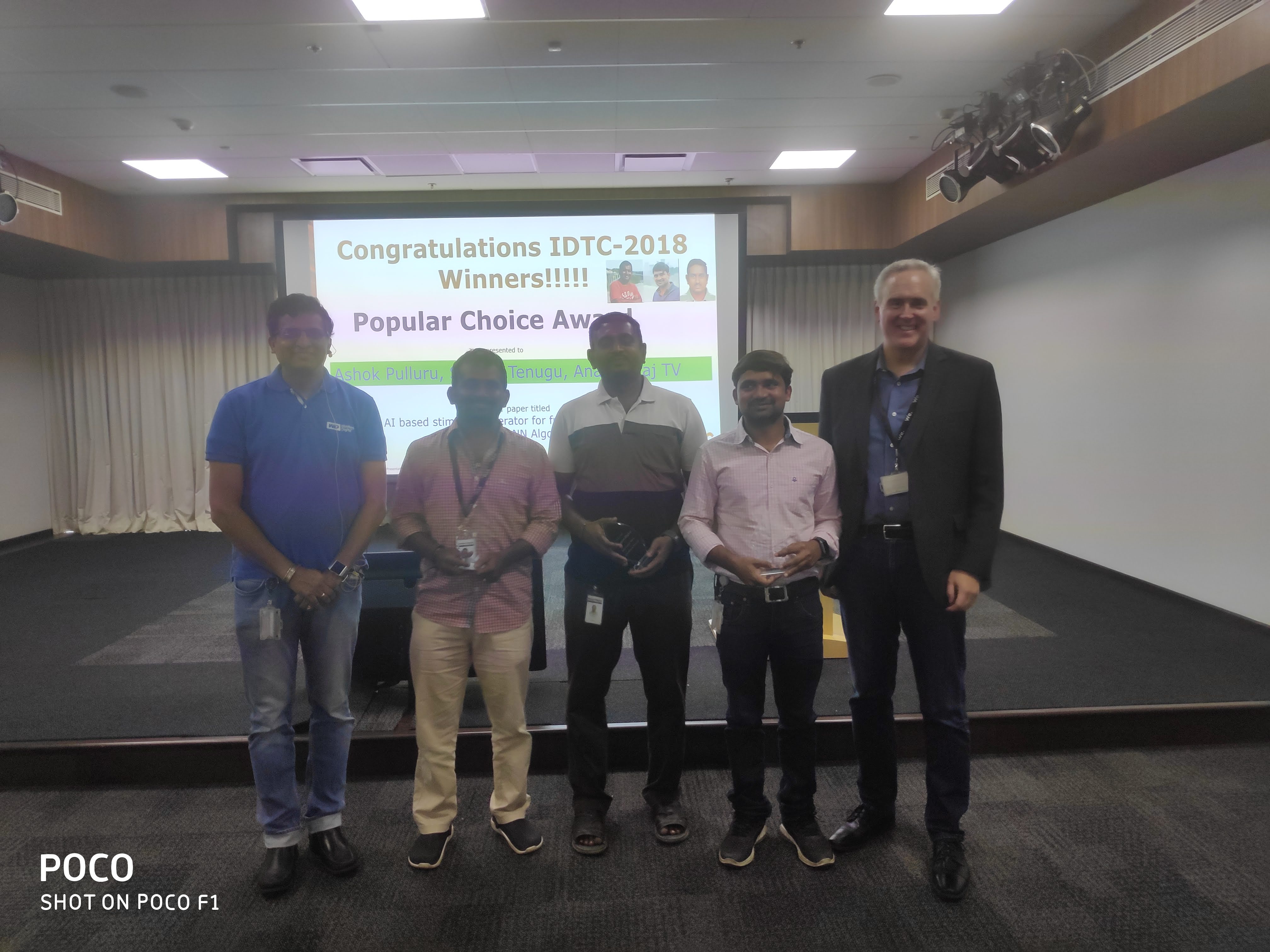

Achievements

Awards

Photos

Contact

Address

San Jose, California

Call

+1-341-345-2659

https://www.linkedin.com/in/anantharajvlsi